Sistemas electrónicos: de la placa al chip

La progresiva disminución de coste y tamaño junto con el aumento de prestaciones de los sistemas electrónicos ha permitido un espectacular crecimiento industrial

Introducción

En el año 1965, en una entrevista de la revista Electronics, el entonces presidente de Fairchild Semiconductor, Gordon Moore, afirmó que el número de transistores integrables por pulgada cuadrada se duplicaba cada año. Algún tiempo después, cuando junto con Robert Noyce se fraguaba la fundación de Intel Corporation, Moore corrigió su afirmación indicando que la densidad de integración se duplicaba cada 18 meses, generándose, así, la que se conoce, desde entonces, como ley de Moore.

La importancia de esta ley marca la evolución de los sistemas electrónicos, ya que conlleva una disminución del coste junto con un incremento de prestaciones que se consiguen, éstas, al aumentar el número de componentes integrados. Esta ley, además, conlleva fuertes implicaciones económicas, hasta tal punto que, para algunos economistas, el apogeo de la economía norteamericana está íntimamente ligado al aumento exponencial de las prestaciones de los ordenadores.

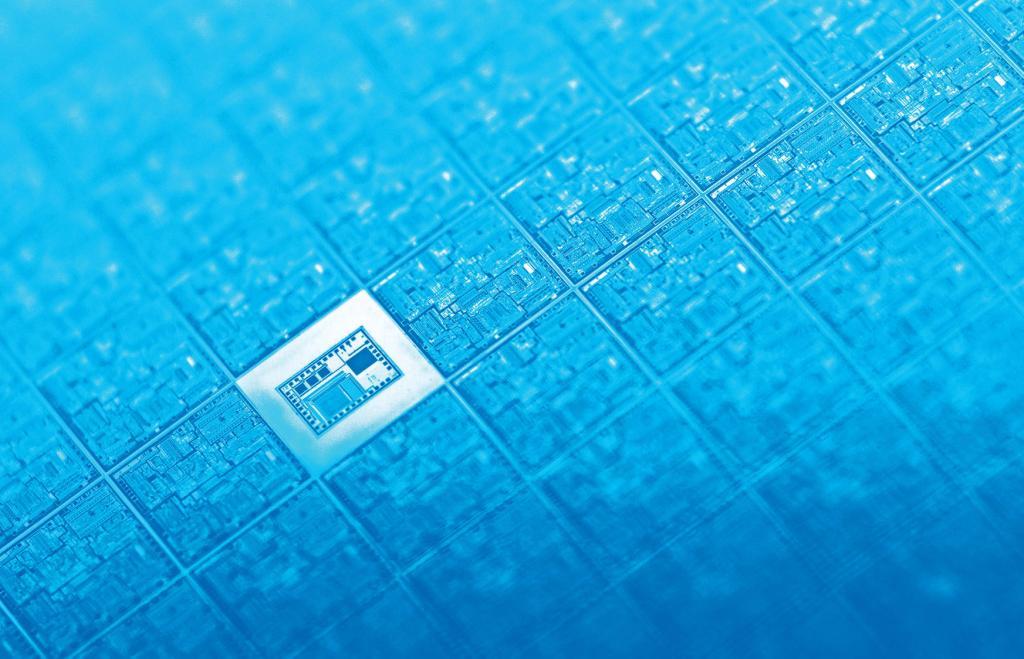

La figura 1 muestra gráficamente la tendencia en la densidad de integración.

A la vista de estos resultados, la pregunta es clara: ¿hasta dónde es capaz la tecnología de mantener este ritmo de crecimiento exponencial de la densidad de integración?

Un poco de historia

En el año 1947, los ingenieros de los laboratorios Bell, John Bardeen, Walter Brattain y William Shockley desarrollaron el dispositivo denominado transistor (acrónimo de TRANSfer resISTOR) de puntas de contacto (figura 2), un componente capaz de cambiar su característica resistiva en función de la corriente inyectada a su electrodo de control.

Este descubrimiento, trascendental para el desarrollo de la electrónica, no tuvo demasiadas implicaciones hasta que en el año 1950 William Shockley, también en la Bell, desarrolló el primer transistor de unión (figura 3), a partir del cual Jack Killby (Texas Instruments, 1958) desarrolló el que se denominó circuito sólido, actualmente circuito integrado, CI, o chip, siendo dicho primer CI un dispositivo de seis transistores de unión sobre un mismo sustrato semiconductor de silicio (figura 3).

Casi al mismo tiempo que Killby desarrollaba el circuito integrado, Jean Hoerni, de Fairchild, en 1959, desarrolló el primer transistor planar de silicio (figura 4), hecho que permitió a esta empresa desarrollar, en el año 1961, el primer circuito integrado planar (un biestable set-reset, figura 4), base de la actual electrónica integrada (microelectrónica), a partir del cual esta empresa comercializó el primer circuito integrado producido masivamente en 1963: el 709, un dispositivo de dos puertas lógicas con cuatro transistores y cuatro resistores cada una de ellas, hito que se considera el inicio de la integración comercial en la que se ha denominado SSI: Small-Scale integration, Integración a pequeña escala.

A partir de este momento, y con la base de la tecnología planar desarrollada, la densidad de integración aumentó espectacularmente. Así, en 1964 algunos chips incluían 32 transistores y en el 1965 el circuito integrado más complejo incluía 64 transistores, momento en que Moore anunció su ley corregida: cada 18 meses se dobla la densidad de integración.

La década de los sesenta se complementa con dos hechos que permiten la evolución de la microelectrónica: el descubrimiento del transistor de metal y óxido semiconductor de efecto de campo, Mosfet, por D. Kahng en los laboratorios Bell, a finales de 1960, y la utilización de programas de ayuda al diseño por ordenador (DAO) a partir de 1967. Estos desarrollos, junto con la utilización de obleas de silicio cada vez mayores (de 300 mm a partir del 1995) permiten desarrollos de circuitos integrados con un número cada vez mayor de transistores y otros componentes. Veamos algunos ejemplos:

- 1971. Intel introduce el primer microprocesador, el 4004: 2.300 transistores.

- 1974. Primer microprocesador de 8 bits, el 8008, con 3.500 transistores.

- 1980. Primer circuito de memoria RAM de 64 kbit: unos 250.000 transistores.

- 1985. Microprocesador i386: unos 500.000 transistores.

- 1992. Microprocesador i486 DX2: 1,2 millones de transistores.

- 1997. Microprocesador Pentium 2. 7,5 millones de transistores.

- 1998. Microprocesador Pentium 3: 28 millones de transistores.

- 2002. Microprocesador Pentium 4: 55 millones de transistores.

- 2004. Microprocesador Itanium 2: 430 millones de transistores.

El lector interesado encontrará en el siguiente enlace información detallada sobre la historia del desarrollo del circuito integrado: http://www.icknowledge.com/history/history.html.

¿Cuál es la base tecnológica que per-mite, actualmente, empaquetar estas cantidades ingentes de componentes en un dispositivo único? ¿Hasta dónde se podrá seguir avanzando en el aumento de la densidad de integración? Estas preguntas merecen una especial atención, ya que son claves para mantener la tendencia de la complejidad creciente de los sistemas electrónicos que se precisan en nuestra sociedad.

El principio de la respuesta a estas preguntas es el proceso que permite fabricar circuitos integrados, su continuación es la problemática asociada a los costes de producción y un aspecto final importantísimo para la respuesta a las mismas se deriva de las posibilidades de encapsulado de componentes que han de permitir, a todas luces, la disminución del peso y volumen de los equipos electrónicos así como una disminución de sus costes productivos. Veamos, someramente, cada uno de estos aspectos.

Fabricación de los circuitos integrados

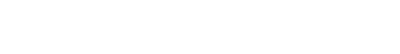

Actualmente, la fabricación de circuitos integrados (CI) o chips, se realiza, mayoritariamente, a partir de una base semiconductora de silicio. Dicha base se obtiene procesando el silicio en bloques cilíndricos, hasta obtener una oblea circular de entre 25 µm y 300 µm, y un grosor de entre 200 mm y 800 mm (figura 5) extraordinariamente pulida y con muy pocas impurezas.

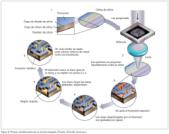

A partir de la oblea primaria, la fabricación del CI se realiza mediante un proceso cíclico de pasos, esquematizado en la figura 6, los cuales se pueden realizar hasta 20 veces, de forma que es posible fabricar muchos circuitos integrados a partir de una única oblea de silicio, a la cual se ha aplicado una capa sensible a la luz o fotoresist (1). Cada ciclo comienza con un patrón determinado, que se proyecta repetidamente sobre la oblea (2). En cada zona donde se proyecta la imagen, se producirá un chip. Se quita la capa fotosensible (3), y las áreas expuestas a la luz ultravioleta se graban al aguafuerte mediante un ataque por gases (4). Estas áreas se bombardean posteriormente con iones (proceso denominado dopaje), creando los diversos transistores y otros dispositivos que forman parte del CI (5). Dichos componentes se interconectan entre sí, mientras que en los ciclos sucesivos se agregan capas de metal y de aislante (6) hasta completar el diseño del circuito integrado.

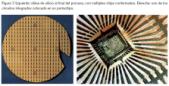

El resultado final es que de la oblea inicial se obtiene una oblea con los chips conformados (figura 7a), los cuales se cor-tan de la oblea formando los denominados dados (en inglés die) o pastillas para, seguidamente, colocarlos en un portador de CI (carrier) o portachip (figura 7) que permitirá el posterior encapsulado

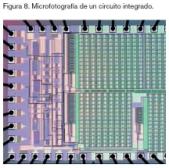

El resultado final puede ser, en algunas ocasiones, realmente sorprendente. A título de ejemplo, para constatar esta afirmación y observar los niveles de proceso que se pueden obtener, se presenta, en la figura 8, un circuito integrado correspondiente a un convertidor de continua-continua realizado en tecnología de 0,5 mm, mientras que en la figura 9 se muestra el detalle de las conexiones externas y de las depositaciones de cobre que las permiten.

Sobre los costes de producción de circuitos integrados

La producción de circuitos integrados es costosa. De hecho, el aumento de la complejidad de los mismos conlleva, necesariamente, un aumento de las prestaciones de la maquinaria de producción (el proceso en sí mismo), lo que a su vez comporta un aumento de costes. Por ello es necesario buscar un equilibrio entre las prestaciones del circuito integrado (dadas por su complejidad) o las funciones que puede realizar, y el precio máximo que los clientes-usuarios del mismo están dispuestos a pagar, cosa que, a su vez, conlleva el cambio en el proceso de producción. Así pues, estamos ante una severa solución de compromiso entre el costo y las prestaciones. ¿Cómo se resuelve este aspecto?

La figura 10 muestra la curva de costes de producción de un circuito integrado mediante un proceso (curva azul) u otro (curva negra). Cada curva se asocia a un proceso de fabricación distinto. En cada caso, existen barreras tecnológicas (puntos T1 y T2) donde un pequeño aumento de prestaciones (u horas de funcionamiento) se consigue únicamente mediante un costo enorme (crecimiento exponencial de las curvas). Por otro lado, las barreras económicas (puntos E1 y E2), marcadas por el precio máximo que el cliente es capaz de admitir, se dan generalmente antes de que se presenten las barreras tecnológicas.

Así, cuando en un proceso (curva azul) se presenta una barrera económica (punto E1) antes de su correspondiente barrera tecnológica (punto T1) es necesario introducir una brecha tecnológica que permita un nuevo proceso de fabricación capaz de desplazar la curva de costos (azul) a una nueva zona (curva negra) donde a igualdad de precio máximo se pueda conseguir un aumento importante de prestaciones o, lo que es equivalente, que manteniendo prestaciones se disminuya el precio.

Se trata, evidentemente, de un equilibrio económico-tecnológico de primera magnitud.

Encapsulados para circuitos integrados

Los procesos de fabricación de circuitos integrados se basan en la actualidad, y a grandes rasgos, en aumentar la densidad de integración a base de disminuir eltamaño de los componentes (como los transistores) lo que permite una disminución de las tensiones de alimentación y un aumento de la frecuencia máxima de trabajo sin un aumento notable de la potencia consumida. Así se habla, por ejemplo, que un determinado CI se ha realizado con una tecnología de 1,5 micras, mientras que otro circuito se ha realizado con una tecnología de 0,9 micras.

Pero ¿a qué dimensión nos referimos al hablar de estas micras?.

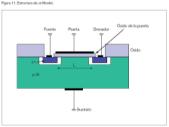

Conforme crece la densidad de integración, en las denominadas tecnologías LSI (Large-Scale Integration, integración a gran escala) y VLSI (Very Large-Scale Integration, integración a muy gran escala), cobra gran importancia la utilización de dispositivos Mosfet (transisto-res de efecto de campo de semiconductor, metal y óxido), debido a su pequeño tamaño, bajos costos de fabricación y baja disipación de potencia. La figura 11 muestra una sección transversal de uno de estos transistores, de utilización en microprocesadores, chips de comunicaciones, memorias y otros sistemas.

La dimensión en micras (1 µm, 10-6 m) utilizada define, directamente, el tamaño del transistor, y se relaciona con la denominada longitud del canal (L en la figura 11), distancia muy próxima al valor del lado del rectángulo de óxido utilizado para aislar el terminal de puerta del dispositivo.

La disminución de este valor permite cumplir los requisitos básicos enunciados tanto por la ley de Moore (figura 1) como los correspondientes a parámetros económicos (figura 10). De hecho, los números hablan por sí solos: el microprocesador 8008, de 1972, incluía unos 3.500 transistores en una pastilla (die) de unos 32 mm2. Si no se hubiese reducido el tamaño de los transistores, un procesador Pentium 4 (2002), que incluye unos 55 millones de transistores, necesitaría una pastilla de casi 500.000 mm2, es decir, una pastilla semiconductora de unos 70 cm de lado en caso de ser cuadrada… sin contar el monstruoso encapsulado que se requeriría. De hecho, en la actualidad se consiguen integrar 50 millones de transistores en una pastilla de unos 150 mm2 (un cuadrado de algo más de 12 mm de lado) con cierta comodidad.

Físicamente, un encapsulado (o paquete, package en inglés) no es más que el soporte físico que actúa de interfaz entre la pastilla semiconductora del circuito integrado (junto con su portador, figura 7) y el cableado impreso (PCB, Printed Circuit Board) sobre el cual se monta (figura 12). De hecho, un chip es inútil sin su encapsulado, ya que el mismo

Es el enlace para la alimentación del circuito integrado

- Canaliza la transferencia de información en el interior del microcircuito y a su exterior a través del PCB

- Es la interfaz para la disipación de calor

- Protege al IC de elementos externos .

Dicho encapsulado puede ser de material plástico o cerámico y, lógicamente, cuanto mayor es la complejidad del circuito integrado que contiene, mayor es la complejidad del encapsulado, lo que muchas veces se traduce en el número de pins (patillas) del mismo. Por lo tanto, existe un paralelismo entre el aumento de la densidad de integración (mayor número de componentes por mm2 del CI) y la complejidad del encapsulado correspondiente (tamaño y número de pins), ya que éste debe ser más fiable cuanto mayor sea la complejidad del microcircuito que contiene.

- SiP. System-in-Package (Sistema en encapsulado). Utilizadas para sistemas complejos multidisciplinares donde pueden existir diferentes tecnologías que no admiten la integración en una única pastilla semiconductora (por ejemplo, visualizadores de cristal líquido, inductancias, memorias y procesadores de señal).

- SoC. System-on-Chip (Sistema en circuito integrado). Utilizada en el caso donde la o las tecnologías utilizadas permitan la integración en una pastilla única.

De esta forma es posible, en la actualidad, disponer de encapsulados de más de 1.000 pins, como, por ejemplo, la FPGA de Xilinx 1704, en un encapsulado de 1.704 pins.

Actualmente, existen dos procedimientos aplicables para los encapsulados de circuitos integrados:

- PTH. Pin-Trhough-Hole (Pin a través de agujero), sistema que permite insertar los pins del encapsulado en el PCB a través de un agujero, uniéndolos al mismo mediante soldaduras realizadas o bien en el lado opuesto al de inserción del CI o bien en ambos lados del PCB.(figura 13).

- SMT. Surface-Mount Technology (Tecnología de montaje superficial), sistema que permite la soldadura directa de los pins del encapsulado en la misma cara del PCB donde reposa el CI (figura 13). Este método es muy ventajoso respecto al PTH ya que permite la ausencia de agujeros en el PCB para la inserción de los chips, lo que aumenta la facilidad en la fabricación, y permite colocar componentes en las dos caras del PCB, lo que se traduce en unas dimensiones menores, disminución de componentes parásitos y aumento en la densidad del cableado impreso.

Los encapsulados de circuitos integrados se realizan, a grandes rasgos, en dos tipos de materiales:

- Plástico. Permite el enlace tanto de pastillas como de hilos conductores, ya que se conforman mediante técnicas de plástico inyectado y moldeado. La pastilla se incorpora rodeada de un marco de plomo (lo que actualmente choca frontalmente con ciertas normativas y recomendaciones, como la europea RoHS Compliance1, que limita los contenidos en plomo, cadmio, mercurio y otros elementos peligrosos en los equipos electrónicos). Son baratos en cuanto a costes de fabricación, pero presentan dos inconvenientes relevantes: su resistencia térmica es elevada (baja capacidad de disipación de calor) y son higroscópicos (absorben la humedad), lo que puede dar lugar a una evaporación instantánea del agua acumulada en caso de calentamiento rápido, lo que, a su vez, puede conllevar un aumento rápido de la presión hidrostática y originar delaminaciones internas o agrietamientos del encapsulado con su correspondiente destrucción.

- Cerámica. Consiste en diversas capas (layers) de conductores separadas por diversas capas de material cerámico, típicamente alúmina (Al2O3). La pastilla semiconductora se coloca en una cavidad y se enlaza a los conductores. Dicha cavidad acostumbra a estar sellada con una tapa metálica. Estos encapsulados son más costosos que los plásticos, y presentan una resistencia térmica mucho menor (mejor disipación de calor), aunque la elevada constante dieléctrica de la alúmina puede provocar retardos de propagación elevados para según qué aplicaciones.

La figura 14 muestra algunos de los encapsulados más populares.

Figura 14. Algunos de los encapsulados de CI más populares. De izquierda a derecha: DIL o DIP (Dual-in-Line o Dual-in-Package), SC70, SOIC (Small-Outline Integrated Circuit), TSSOP (Thin Shrink Small Outline), LCC (Lead Chip Carrier) y TQFP (Thin Quad Flat Package). Generalmente, dichas designaciones se complementan con el número de pins del encapsulado, anteponiéndose una «P» en caso de encapsulado plástico. Así, la figura muestra, entre otros, los encapsulados PDIP14 (el primero, plástico) y el TQFP32 (el último, cerámico). (Fuente: Kart Rinne, Universidad de Limerick).

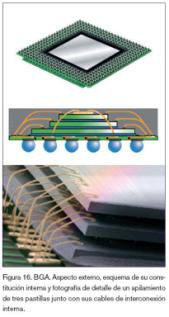

Todos los encapsulados anteriormente citados responden a una necesidad tecnológica de integrar una única pastilla semiconductora. No obstante, el aumento de la densidad de integración y la necesidad de utilizar dispositivos más complejos hacen que, últimamente, se desarrollen otros tipos de encapsulados que permitan acoger estas necesidades crecientes. Quizá, entre todos ellos, destaque el denominado BGA (Ball Grid Array, de traducción similar a “bolas dispuestas en rejilla”), de aspecto indicado en la figura 15.

En este tipo de encapsulados los pins se han sustituido por bolas de material anisotrópico fácilmente fundible, lo que permite la soldadura sobre el PCB de una forma cómoda. La tecnología actual per-mite BGA de más de 1.700 pins. Además, su constitución permite una inspección rápida de la integridad de las soldaduras mediante radiografías.

Este tipo de encapsulados permite un apilamiento (stack) de distintas pastillas semiconductoras en su interior, interconectadas entre sí, de forma que se minimiza el número de puntos de conexión externos, aumentándose así la densidad de integración, al tiempo que se permite la coexistencia, en el interior del encapsulado, de diversas tecnologías constructivas.

La figura 16 muestra un encapsulado BGA, con el grafismo de su construcción y una microfotografía de un circuito concreto (cortesía de Intel Corporation), en el caso concreto que las pastillas se conecten internamente mediante cables conductores (wire-bonded).

De esta forma, con la introducción de encapsulados avanzados como el BGA, se ha podido aumentar la densidad de integración de los sistemas electrónicos. La figura 17 muestra una placa base de un sistema microcomputador del año 1981 (considerado por aquel entonces de alta densidad), mientras que la figura 18 muestra la placa de un sistema electrónico de comunicaciones, del año 2000, considerado de baja densidad. La diferencia salta a la vista en estos dos casos de los que se denominan SoB (System-on-Board, sistemas en placa).

No obstante, la densidad de integración sigue aumentando, y, sobre todo en equipos portátiles, no es posible utilizar placas como las mostradas debido a sus dimensiones excesivas. No debe cundir la alarma. La tecnología actual per-mite la sustitución de estas placas por otras mucho menores. Gracias a la utilización de encapsulados de elevada densidad, y a los circuitos integrados actuales, es posible pensar en la idea de “un chip, un sistema”.

La sustitución de las placas por circuitos integrados únicos

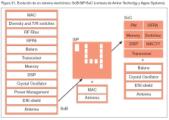

La electrónica de consumo, sobre todo en lo que se refiere a equipos portables, impone, cada vez más, restricciones en cuanto a tamaño, peso y consumo de los sistemas comerciales que, a su vez, han de incorporar cada vez más funciones. La figura 19 muestra las funciones que puede incorporar un teléfono móvil de la siguiente generación de estos dispositivos.

Para conseguir esta densidad de funciones en unos sistemas cada vez más reducidos, la tecnología actual utiliza tres campos de actuación bien concretos:

- Las baterías, con mayor densidad de carga y mayor duración que la generación anterior, junto con sus circuitos de carga y descarga (smart chargers).

- La distribución racional de la energía utilizada por dichos sistemas electrónicos, en lo que se denomina power management.

- La tecnología de los circuitos integrados y sus encapsulados.

Prescindiendo de los dos primeros aspectos, dediquemos algunas líneas al último, y no por ello menos importante, de los mismos.

Flip-Chip

Dentro de las tecnologías emergentes de encapsulados para circuitos integrados, cobra cada vez mayor relevancia la denominada flip-chip, introducida no hace mucho por algunos fabricantes como Altera, Intel o Amkor Technology.

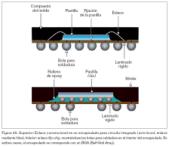

Flip-chip es un método de interconexión de pastillas de CI en el interior de un encapsulado. Así, en un encapsulado normal, las pastillas se interconectan mediante cables conductores muy delgados (wire-bond), mientras que en la tecnología flip-chip las interconexiones entre pastillas se realizan mediante bolas de material conductor anisotrópico para soldadura, de unas 100 µm de diámetro) que enlazan directamente las pastillas en el portachips. Esquemáticamente, la diferencia entre ambos procedimientos se muestra en la figura 20 (cortesía de Amkor Technology).

Entre las ventajas inherentes a la tecnología flip-chip citamos:

- Reducción de las inductancias en los caminos de señal, debido a que las vías de interconexión (bolas contra cables) son mucho más cortas, del orden de 0,1 mm contra 1 mm a 5 mm.

- Mayor inmunidad al ruido, ya que se evitan los “largos” caminos que debe recorrer la señal en los enlaces convencionales mediante hilo (o cable).

- Mayor densidad de puntos de interconexión, ya que en la tecnología flip-chip se puede emplear la práctica totalidad de la base de la pastilla, mientras que la utilización de cables de interconexión restringe la misma a su periferia.

- A igualdad de puntos de interconexión se disminuye el tamaño del encapsulado, permitiéndose, así, una mayor frecuencia de trabajo del sistema y un consumo energético menor. Asimismo, se permite el apilamiento de diversas pastillas semiconductoras unidas mediante bolas anisotrópicas para soldadura.

Así, el flip-chip es el puntal tecnológico que ha de permitir el paso de los sistemas en encapsulado único (SiP) a los sistemas en chip único (SoC), de igual forma que la evolución de los encapsulados permitieron el paso de los sistemas en placa (SoB) a los SiP.

Del SoB al SoC

La figura 21, cortesía de Agere Systems y de Amkor Technology, muestra la tendencia evolutiva de los sistemas electrónicos en el caso concreto de un sistema de comunicaciones inalámbrico (Wi-Fi).

Así, a finales de la década de los noventa era factible la comercialización de este sistema (SoB, System-on-Board) en una placa de cableado impreso con múltiples encapsulados que permitía incluir todas las funciones requeridas para ese sistema electrónico concreto. La evolución de los encapsulados para circuitos integrados permitió, sobre el año 2003, la inclusión de la mayor parte de funciones en un encapsulado único (SiP, System-in-Package), reduciéndose el tamaño del mismo en una escala 1:12. En el año 2005, la disminución del sistema se consigue mediante la inclusión de muchas de las funciones en un único circuito integrado, lo que permite una reducción en el tamaño en una proporción 1:10 en comparación al estadio precedente (SiP).

Típicamente, un SiP (System-in-Package, sistema en encapsulado único) consiste en la combinación de diversos circuitos integrados, enlazados mediante wire-bond o flip-chip, junto con algún componente pasivo, en un encapsulado comercial único, de forma que éste pueda utilizarse individualmente o como parte de una placa más compleja formando, por sí mismo, un módulo funcional complejo (véase la figura 12 con el encapsulado SiP del procesador Itanium abierto). Así, es posible conseguir sistemas que funcionen a mayores velocidades y con un menor consumo energético, con un ahorro de hasta un 90% en el número de componentes externos en comparación con el mismo sistema basado en SoB.

Sistemas adecuados para su comercialización como SiP son, actualmente, entre otros, las tarjetas de memoria de alta capacidad, las cámaras CMOS digitales para fotografía, convertidores estáticos CC-CC, controladores para tarjetas gráficas, sistemas de entrada-salida o sistemas Wi-Fi.

La figura 22 muestra un SiP típico.

Así, la utilización de los SiP permite conjuntar, en un encapsulado único, diversas tecnologías y encapsulados para comercializar productos en los que se han optimizado el coste, el tamaño y sus prestaciones, exigencias de la demanda actual en, por ejemplo, la electrónica de con-sumo.

A partir de los SiP, es posible avanzar hacia los SoC, donde los sistemas electrónicos estarán confinados no en un encapsulado único sino en una única pastilla semiconductora.

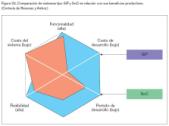

La tecnología actual queda resumida en la figura 23 (cortesía de Amkor-Semico) que muestra que las tecnologías SiP y SoC no son mutuamente excluyentes, y que cada una introduce diversos beneficios:

- SiP. Flexibilidad, ciclo de desarrollo del producto corto, capacidad de integración de diversas tecnologías en un encapsulado único, bajo nivel de ruido y menor costo del sistema.

- SoC. Altas prestaciones (utilizando tecnologías poco dispersas), reducción drástica del área total utilizada y coste del dispositivo aún más bajo.

De hecho, algunos SiP actuales incluyen algún SoC (figura 22), permitiéndose, así, que las funciones que sean fácilmente integrables se implementen mediante SoC y éstos formen parte del SiP, siendo ésta la base tecnológica actual que ha de permitir, en un futuro próximo, la sustitución de estos SiP por SoC como eje para cumplir con la aun vigente ley de Moore.

Comentarios finales

La creciente demanda en las prestaciones de los sistemas electrónicos obliga a un seguimiento industrial de la aún vigente ley de Moore. En este sentido, no es suficiente contar con el aumento exponencial de la capacidad de integración en silicio, o en otros materiales semiconductores, sino que es necesario contemplar otros factores colindantes, como los encapsulados para componentes integrados o las técnicas que permiten el mejor aprovechamiento de la energía disponible, almacenada en las baterías de los sistemas portables.

En este artículo se ha pretendido dar una visión evolutiva de las tecnologías emergentes que permiten mantener este crecimiento exponencial que se traduce en la migración de los sistemas electrónicos en placa (SoB) hacia los sistemas electrónicos en circuito integrado (SoC). Sólo el tiempo dirá dónde está el límite de la tecnología actual.

Bibliografía

Spooner, John. Does Moore’s Law no Longer Apply? ZDNet, 2000.

Tuya, Melisa. Todo lo que quiso saber sobre la ley de Moore y nun ca se atrevió a preguntar. Baquia Knowledge Center (www.baquia.com), 2000.

Haviland, David B. The Transistor History. Artículo en www.nobelprize.org.

Haviland, David B. The History of Integrated Circuit. Artículo en www.nobelprize.org.

Haviland, David B. Integrated Circuit. Artículo en http://en.wikipedia.org.

Haviland, David B. The History of Integrated Circuit. http://www.icknowledge.com.

Haviland, David B. Texas Instruments Interactive Time-line. A partir de los contenidos en la URL http://www.ti.com/ corp/docs/company/history/interactivetimeline.shtml.

Haviland, David B. Silicon Wafers. Compart Technology a partir de la información en la URL www.compart-tech.co.uk/siliconwafers.html.

Haviland, David B. Integrated Circuit Process. Animación en flash en http://www.appliedmaterials.com /HTMAC/ HTMACanimation-full_06142006.swf.

Haviland, David B. Top-Down Nanotechnology. Información de la Universidad de Delft (med.tn.tudelft. nl/…/nanoscience/week3/3.html).

Haviland, David B. Chip Gallery. Información de la Universidad de Arizona (www.ece.arizona.edu/~ma/ chip.htm).

Haviland, David B. Olympus Microscope Integrated Circuit Gallery. Información de la URL http://www.mic-d.com/gallery/chips/index.html.

Haviland, David B. Renesas Technology ic Packaging Data Book, en www.renesas.com.

Haviland, David B. Nec Packages. Nipon Electric Corporation, a partir de la información contenida en la URL http://www.necel.com/pkg/en/index.html.

Del Álamo, Jesús A. Microelectrónica de SI: de la era de los ordenadores a la era de Internet. Novática, junio-julio 2000.

Del Álamo, Jesús A. Flip-Chip Packaging Technology Solution. Amkor Technology (www.amkor.com).

Scanlan, Chris. System-in-Pakage. Flexibility in Integration. Amkor Technology. Conferencia en Convergence and Connectivity, 2003.

Morrison, Joe. Moving to Package Desing from PCBS. Cadence Design Inc, 2003.

Banerjee, Koushik. Microprocessor Package. The Key Link in the Chain. Intel Corporation, 2003.

Park, J y Moll, C. Advaned IC packeging. A Technology Overview. Cadence Design Inc, 2004.

Rossetti, Nazzareno. Managing Power Electronics. John Wiley & Sons, 2006

Claasen, Theo A.C.M. An Industry Perspective on Current and Future of the Art in System-on-Chip (Soc) Technology. Proceedings of the IEEE, Vol 94. Junio de 2006.